The circuitry described in this section performs the following functions:

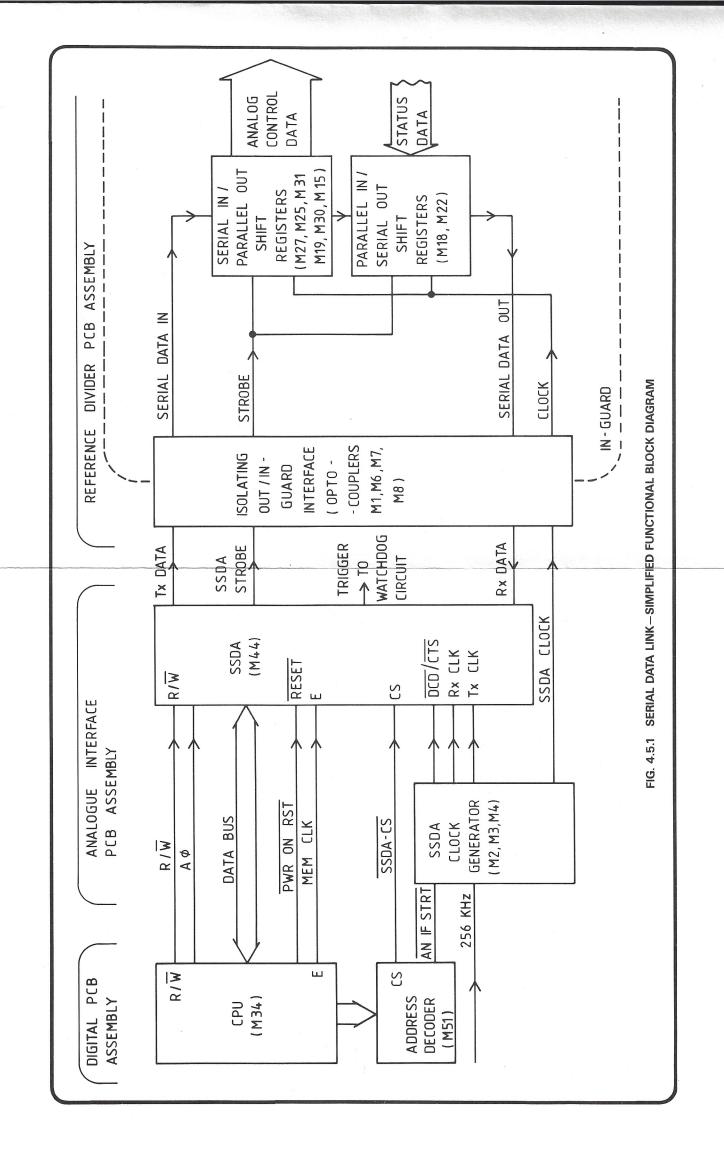

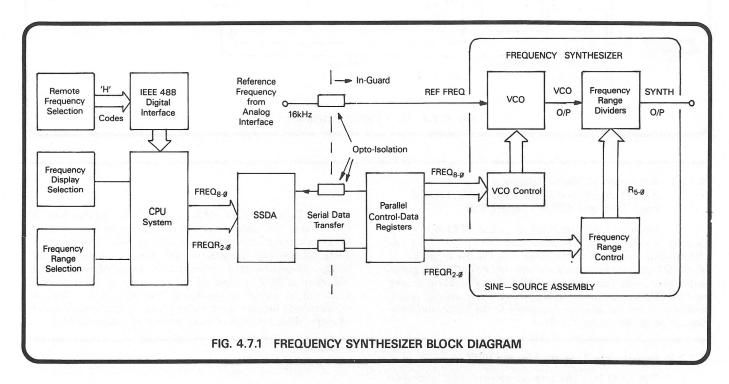

(1) Provides a two-way interface via a serial data link between out-guard digital processing and in-guard analog control circuitry on the reference divider pcb. (See Fig. 4.5.1).

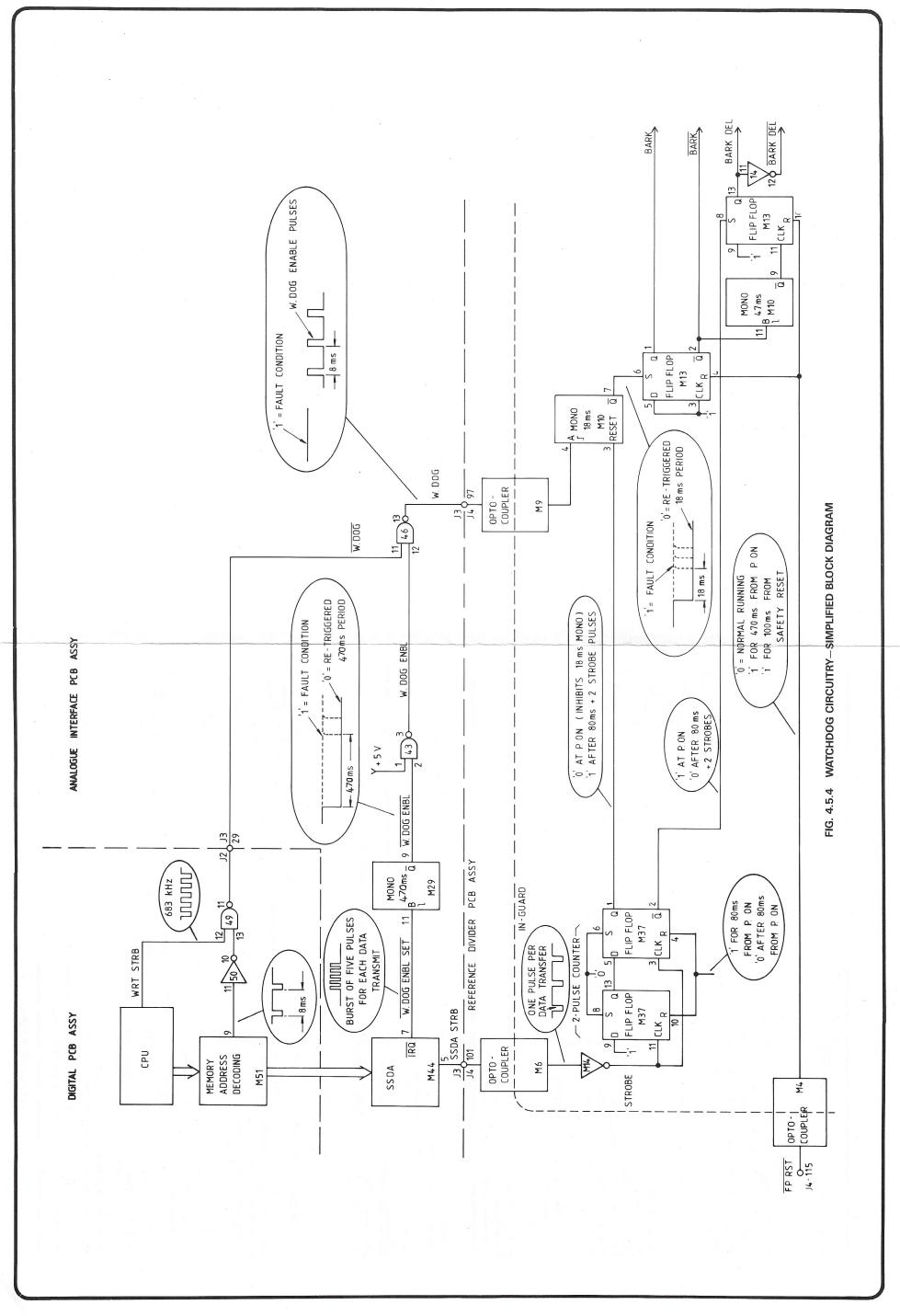

(2) Monitors the CPU operation, serial transfer, digital supply failure and restart operations (watchdog), imposing a controlled safety default condition if there is a danger of losing digital control of the analog functions.

A manual reset of the safety monitor is provided on the front panel. (See Fig. 4.5.4).

#### 4.5.1 General

Safety and Control information is input from Digital (400534) and Front (400533) Assemblies to out-guard circuits located on the Analog Interface Assembly (400570), processed and transferred across the 'Guard' isolation barrier to in-guard circuits in the Reference Divider Assembly (400535). After further processing in the Reference Divider Assembly, safety and control information is output to the following assemblies:

Sine Source Assembly (400446), AC Assembly (400447), PA Assembly (400450), Output Control Assembly (400550), Current Assembly (400555), and High Voltage Assembly (400565).

Certain selected 'Status' signals, originating in the analog assemblies, are returned to the CPU during the data transfer. Thus, the data link forms a continuous loop, as shown in Fig. 4.5.1.

#### 4.5.2 Serial Data Transfer (Fig. 4.5.1)

(Circuit Diagrams: 430534 Page 7.2-2, 430570 Page 7.3-3, 430535 Page 7.4-4 and Page 7.5-5)

A bi-directional serial data link passes information across the guard isolation screen; conveying CPU instructions to control the in-guard analog circuitry, and transferring critical status signals from the guarded circuits back to the CPU.

The link is managed by a synchronous serial data adapter (SSDA) which, having first been loaded with three bytes of control instructions by the microprocessor; transmits

the resultant 24-bit word across guard one bit at a time, via its  $\mathsf{Tx}\ \mathsf{DATA}\ \mathsf{channel}.$

The 48 bits necessary to control the analog circuitry thus require two successive 24-bit transmissions.

Simultaneously with each 24-bit transmission, the SSDA receives a 24-bit word via its Rx DATA channel, enabling the CPU to obtain the status of the analog functions.

#### 4.5.2.1 The Transfer Cycle (Fig. 4.5.1)

The CPU uses an address-code signal AN I/F STRT (Analog Interface Start) to initiate each 24-bit shift, by triggering a separate clock generator (M2, M3, M4) which produces a burst of 24 clocks per shift. Data is clocked in a serial string through a continuous loop comprising:

the 48-bit, serial in/parallel out, analog control shift register;

the 16-bit, parallel in/serial out, status shift register; back to the SSDA receiver (Rx DATA).

The serial data string is correctly located after two 24-bit shifts, so then the SSDA generates a strobe pulse which:

(1) Transfers the data present in the serial data string of the six 8-bit analog-control shift registers (M27, M25, M31, M19, M30, M15) into their enabled parallel output registers and onto the analog control bus.

When the strobe ends, further transfer is disabled and the registers' output data is latched.

(2) Injects the status data at each of the parallel inputs of the two 8-bit status shift registers (M18, M22) into corresponding locations in the serial data string.

When the strobe ends, the parallel inputs to the status registers are disabled.

After the strobe pulse, the CPU initiates a further circulation of serial data (including the status data), in order to obtain the status data and return the analog control bits to the SSDA Rx DATA register for parity checking by the CPU.

This extra (confirmatory) circulation requires three more 24-bit shifts, so a complete data transfer consists of five shifts. If no error is detected, the SSDA provides a triggerenable to allow updates to prevent activation (BARK) of the watchdog circuits.

If an error is detected on the first transfer, the CPU activates a second complete transfer, and then a third if an error is detected on the second. If the error persists after the third transfer, the trigger-enable is withheld, and the instrument will shut-down under the control of the watchdog safety monitor.

All interfacing between out-guard and in-guard circuits is achieved using electrically-isolating opto-couplers.

#### 4.5.2.2 Data Transfer Organisation

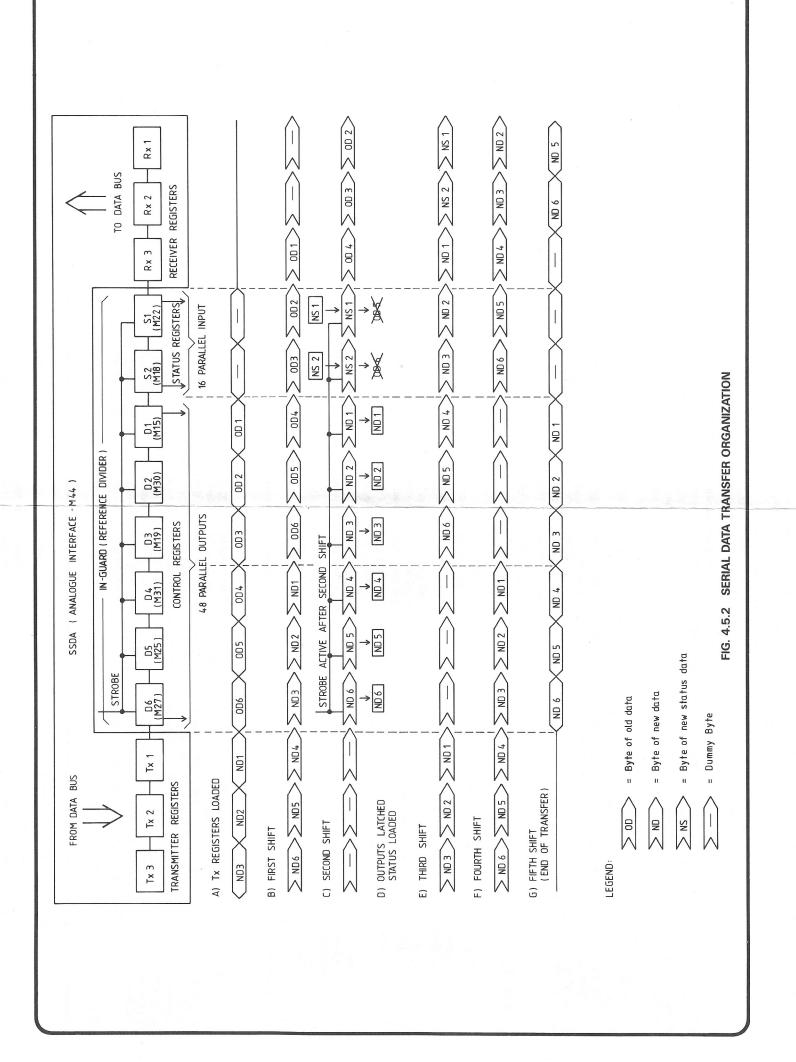

(Fig. 4.5.2)

Data is transferred serially via the SSDA, control registers and status registers as directed by the CPU.

The exchange of data between the CPU and SSDA is made on the 8-bit instrument data bus, each exchange comprising three bytes (24 bits) of parallel data.

The shifts of serial data through the in-guard circuit are synchronized by clocks which are controlled from the CPU, and the SSDA Rx return registers are cleared when read by the CPU.

Once the in-guard serial data is correctly positioned at the inputs to the control registers, the SSDA generates a strobe which enables its transfer to the parallel outputs of the control registers. The same strobe enables injection of the data on the parallel inputs of the status registers into the serial data string.

The transfer operation requries five serial data shifts, each of three bytes, through the registers. During this operation: the control registers are loaded with bytes of new data (ND); the status registers are loaded with new status data (NS); and the whole of the ND and NS data is returned to the CPU, which:

a. verifies that the analog control bits of the serial data string return to the SSDA Rx DATA register without error. This confirmation indicates that at least, the correct bit pattern was applied to the analog control register inputs at the time the strobe was generated.

and

b. acts upon the status data received.

#### 4.5.2.3 Transfer Sequence

The sequence of events in the transfer operation is as follows, refer to Fig. 4.5.2:

- (A) Three bytes of new data, ND1, 2 and 3 are loaded into the SSDA transmitter registers; this data is destined for control registers D1, 2 and 3. The SSDA receiver registers were cleared when last read by the CPU.

- (B) A burst of 24 clock pulses, initiated by the CPU, shifts all data three bytes to the right. After the shift is completed, the transmitter registers are loaded with new data bytes ND4, 5 and 6 (destined for control registers D4, 5 and 6). During this period, no transfers are made between the serial data string and the parallel control or status registers.

- (C) A second burst of 24 clock pulses again shifts all data three bytes to the right. New data bytes ND1 to 6 are now correctly positioned in control registers D1-D6. After completion of the shift, three dummy bytes are loaded into the transmitter registers. Old data (OD) in the receiver register is ignored.

- (D) With new data bytes ND1 to 6 correctly located, the SSDA generates a strobe pulse. This pulse:

- latches the 48 bits of bytes ND1 to 6 at the parallel outputs of control registers D1 to 6;

- (2) enables the parallel inputs of status registers S1 and 2, loading two new status bytes NS1 and 2 and clearing old data OD5 and 6 from the registers.

- (E) A third burst of 24 clocks again shifts all data three bytes to the right. The CPU reads bytes NS1, NS2 and ND1 from the SSDA receiver registers (the CPU may take immediate action on NS returns). After the shift is complete, new data bytes ND1, 2 and 3 are re-loaded into the transmitter registers.

- (F) A fourth burst of 24 clocks again shifts all data three bytes to the right. The CPU reads bytes ND2, 3 and 4 from the receiver registers. After the shift is complete, new data bytes ND4, 5 and 6 are re-loaded into the transmitter registers.

- (G) A fifth burst of 24 clocks again shifts all data three bytes to the right. Bytes ND5 and 6 are read from the receiver registers. The CPU has now read all new data and status bytes and the transfer sequence ends. If an error is detected between new data transmitted and new data received, the transfer process is repeated; three attempts are allowed before a fault condition is declared.

# 4.5.3 Synchronous Serial Data Adaptor (Circuit Diagram 430570 Page 7.3-5)

#### 4.5.3.1 SSDA Initialization

When power supplies are first switched on or an external reset EXT RST is applied, the signal PWR ON RST (Power On Reset) is held at logic-Ø for approximately 8ms.

During this period, the SSDA is latched in a reset condition to prevent erroneous output transitions at its Tx and Rx interfaces; the internal transmit registers are inhibited to prevent the loading of data from the data bus and the SSDA strobe output is held at logic-1.

After PWR ON RST returns to logic-1; the latches, registers and SSDA strobe are cleared in software, during the initialization routine.

#### 4.5.3.2 Parallel Data Input From CPU

The conditions for parallel data on the data bus to be accepted by the SSDA are as follows:

- (1) Chip-select SSDA CS at logic-Ø.

- (2) Read/Write command R/W at logic-Ø. This controls the direction of data flow via the Data Bus through the SSDA input/output port. When R/W is at logic-Ø, data on the Data Bus is written into a selected register within the SSDA.

- (3) The memory clock 'MEMCLK' 682.6kHz square wave is present to synchronize the SSDA operating cycle to that of the CPU.

With input conditions present as above and register address bit Ao at logic-1, the SSDA accepts data from the data bus into an internal 3-byte FIFO register. This data is entered over several MEMCLK cycles and stored in the FIFO register in readiness for serial transmission from the SSDA.

Software programming of the SSDA is performed when the address bit Ao is at logic-Ø. For details of 'Control Byte' operation, refer to Motorola 6852 data sheet.

#### 4.5.3.3 Parallel Data Output to CPU

The conditions for data to be read back from the SSDA on to the data bus are as follows:

- (1) Chip-select SSDA CS at logic-Ø.

- (2) Read/Write command R/W at Logic-1.

- (3) Memory clock, MEM CLK, present.

The data read from the SSDA may be from one of two sources, selection being made by address bit Ao:

With Ao at logic-1, received data from the serial data input FIFO is transferred to the data bus.

With Ao at logic- $\emptyset$ , the CPU reads an internal SSDA status register.

#### 4.5.3.4 Serial Data Transmission

Serial data transmission is controlled by the CTS (clear to send) input to the SSDA. Transmission is inhibited by CTS at logic-1, and enabled when CTS is set to logic-Ø by the CPU address-code signal AN I/F STRT. The first serial bit is transmitted by the negative transition of the first full positive Tx clock pulse (256 kHz) after CTS has been set to logic-Ø. CTS is held at logic-Ø by the AN I/F STRT latch for the duration of 24 full Tx clock pulses, thus enabling the serial shift transmission of the 24 data bits from the Tx Data FIFO in the SSDA.

#### 4.5.3.5 Serial Data Reception

Serial data is received by the SSDA, controlled by the DCD (data carrier detect) level and clocked by Rx CLOCK. DCD is common to the transmit control CTS so that transmission to, and reception from the serial/parallel shift registers is synchronous. Both Rx CLOCK and Tx CLOCK have the same frequency but Rx CLOCK is inverted with respect to the latter. The first bit arriving at its Rx DATA input is clocked into the SSDA Receive FIFO register on the positive transition of the first full Rx clock after DCD is set to logic-Ø.

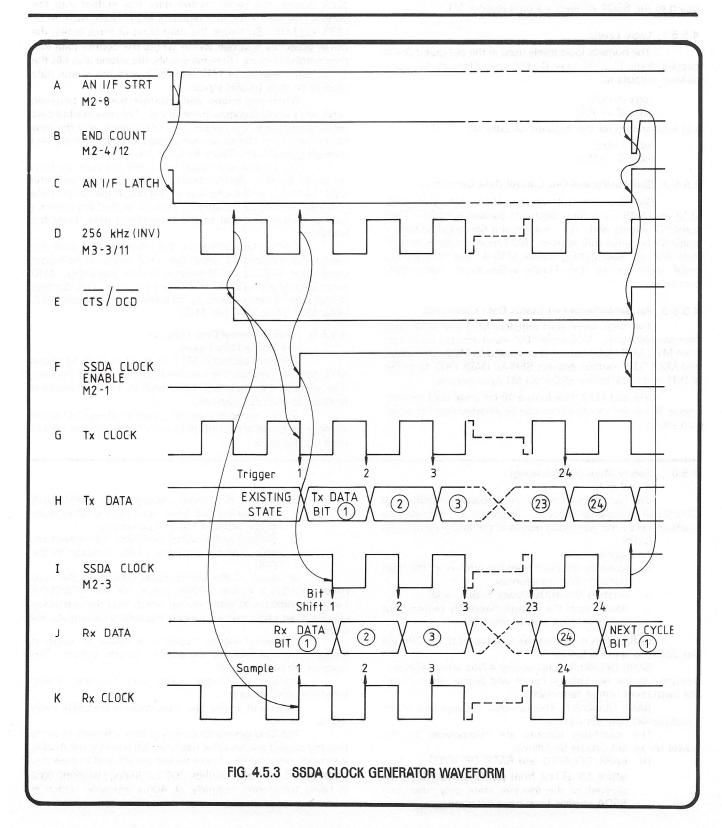

#### 4.5.4 SSDA Clock Generation

Serial data is transmitted and received in bursts of 24 data bits. Three clocks are used to time the flow of bits, ensuring that:

- (1) Data has time to settle before being clocked along the shift registers.

- (2) The first Rx data sample is taken before it is lost by the first bit-shift.

- (3) Subsequent Rx data has time to settle before being sampled by the SSDA.

- (4) Exactly 24 bits are shifted in each burst.

# 4.5.4.1 SSDA, Tx and Rx Clock Action (Fig. 4.5.3)

The three clocks are derived from the 256 kHz square wave output from the 13-bit counter (Circuit Diagram 430570 Page 7.3-2): The 256 kHz squarewave is used directly as 'Tx clock' into the SSDA. The negative transition of the first full positive pulse after CTS is set to logic-Ø; triggers the first serial Tx data bit setup (Refer to Fig. 4.5.3 Waveforms G and H).

'Rx clock' is an inverted version of the 256 kHz squarewave. The positive transition of the first full Rx clock cycle, after  $\overline{DCD}$  is set to logic-Ø; triggers the SSDA to sample the first Rx data bit before the first SSDA clock has triggered the shift registers. (Refer to Fig. 4.5.3 Waveforms K and J).

'SSDA clock' is also an inverted version of the 256 kHz squarewave. The inversion allows approximately 2ms of data setup time for all serial data bits prior to clocking the data along the shift registers. SSDA clock is gated at M2-3 by the action of M3-12 to ensure that the first Rx data is sampled before it is lost by the first bit-shift. 24 SSDA clock pulses are counted by M4, allowing 24 bits to be shifted before resetting the Analog Interface Start latch M2-11 (TP3) to logic-1. (Refer to Fig. 4.5.3 Waveform I).

#### 4.5.4.2 SSDA Clock Circuitry

(Circuit Diagram 430570 Page 7.3-3)

The following paragraphs describe the action of the SSDA clock generator circuitry.

The action of the SSDA clock generator is initiated by the command AN I/F STRT from the CPU. This occurs after the parallel data has been loaded into the SSDA transmit registers from the data bus. The logic-Ø pulse of AN I/F STRT sets flip-flop M2-10/11 to give a logic-Ø at TP3 which then:

- (1) Sets the D input level of flip-flop M3-5;

- (2) Removes 'set' to enable shift register M3 at M3-6 and M3-8;

- (3) Removes 'reset' to enable counters M4 at M4-7 and M4-15.(Refer to Fig. 4.5.3 Waveforms A and C).

At the next rising edge of the inverted 256 kHz (Rx clock) from M43-8 after  $\overline{\text{AN I/F STRT}}$ , the shift register M3 is clocked but only M3-1 'Q' output changes state to logic- $\emptyset$ . This is applied to the SSDA  $\overline{\text{CTS}}$  and  $\overline{\text{DCD}}$  inputs, thus releasing the inhibits on the SSDA transmit and receive registers.

(Refer to Fig. 4.5.3 Waveforms D and E).

At the next (second) rising edge of the clock to M3, M3-12 changes to logic-1. This allows NAND M2-3 to pass 256 kHz clock pulses via buffer M5-12 to the Reference Divider Assembly as the clock which shifts the serial data string along the analog-control and status registers.

(Refer to Fig. 4.5.3 Waveforms D, F and I).

The 256 kHz clock at NAND M2-3 is applied to the 4-bit up-counter clock input at M4-1, each rising edge causing the counter to increment by 1.

The divide-by-16 output M4-6 is applied to the enable input at M4-10; the falling edge of this output occurs at count-16 and increments the second counter to give, at M4-11, a logic-1 output. At count-24, M4-6 changes again to logic-1, and together with M4-11 output, gives a logic-Ø from NAND M2-4, causing the following actions:

- (1) Flip-flop M2-12 is reset to give logic-1 at TP3.

- (2) The logic-1 at TP3 sets shift register M3 to give:

- a. logic-1 at M3-1, thus inhibiting  $\overline{DCD}$  and  $\overline{CTS}$ ;

- b. logic-Ø at M3-12, disabling NAND M2-3 and thus stopping any further SSDA clocks.

- (3) The logic-1 at TP3 resets the up-counters M4 causing:

- a. the counter outputs to fall to logic-Ø, inhibiting further counting;

- b. NAND M2-5 to rise to logic-1, re-setting flip-flop M2-12 to prepare for the next AN I/F STRT input.

(Refer to Fig. 4.5.3 Waveforms I, B, C, E and F).

#### 4.5.5 Serial/Parallel Data Converter

(Circuit Diagram 430535 Pages 7.4-4 and 7.4-5)

Serial control data transmitted from the SSDA (Analog Interface Assembly), together with their control signals (SSDA strobe and SSDA clock), enter the Reference Divider Assembly via the Mother Assembly.

The data and signals cross the isolation barrier through opto-isolators M6, M7 and M8 into guard.

Serial control and status data is returned out of guard to the SSDA receiver via opto-isolator M1.

#### 4.5.5.1 Logic Levels

The nominal logic levels used in the out-guard SSDA circuits (logic-1=+5V, logic- $\emptyset$ =0V) are offset at the opto-isolator outputs to:

logic-1=10V, logic- $\emptyset$  = -15V;

and level-shifted for the in-guard circuitry to:

logic-1=0V,  $logic-\emptyset = -15V$

#### 4.5.5.2 Serial-In/Parallel-Out Control-Data Convertors

Six 8-bit serial shift registers M27, M25, M31, M19, M30 and M15 each have latchable parallel outputs. Their serial "D" inputs and "Q's" outputs are cascaded to form a single 48-bit serial shift register. M27 receives 'serial data in' from M8 via level-shifting buffer M36-4, and M15 passes serial data on to the Parallel-in/Serial-out Status-Data converters.

#### 4.5.5.3 Parallel-In/Serial-Out Status-Data Converters

Two 8-bit serial shift registers M18 and M22 each have parallel inputs. M18 serial "Ds" input accepts serial data from M15; M18 "Q8" output is cascaded to M22 "Ds" input; and M22 "Q8" output delivers SERIAL DATA OUT to buffer M11-11 and back to the SSDA via M1 opto-isolator.

M18 and M22 thus form a 16-bit serial shift register whose 16 parallel inputs states can be inserted into the serial data string.

#### 4.5.5.4 Serial Data Cycling

The serial data, organized in five blocks of three bytes (Refer to Section 4.5.2.2) is accompanied by synchronized bursts of 24 clocks. The output from optocoupler M7 is buffered via level-shifter M36-2 and then inverted at M14-6. The timing of the positive clock edges allows all bits of serial data (distributed throughout the shift registers) to stabilize before being clocked on.

After the CPU has generated two bursts of data and clock pulses, the serial control data has shifted into the correct positions in control registers M27, M25, M31, M19, M30 and M15. So before the third burst of three bytes, the SSDA produces a strobe which writes the control data into their parallel outputs. Simultaneously, the strobe also fills the 16-bit serial register of M18 and M22 with the status data present on their parallel inputs.

When the strobe ends, further transfers between serial and parallel registers are disabled. The new control data remains latched in the parallel control registers, and the new status data is in the serial status register ready for shifting through guard to the SSDA Rx DATA register.

The control and status bits in the registers are then circulated by three further bursts of clock pulses, until the CPU has read both the new status data and all the control data that were written by the strobe. Verification that the returned control data is identical to the transmitted data, ends the transfer.

If after three attempts, the returned data does not match the transmitted data; the CPU omits to re-trigger monostable M10 in the Reference Divider Assembly. M10 times out and allows BARK DEL to go to logic-Ø. This disables the 48 control data outputs by 'tri-stating' the registers M27, M25, M31, M19, M30 and M15.

# 4.5.5.5 Parallel Control-Data Outputs and Status-Data Inputs

The data latched in M27, M25, M31, M19, M30 and M15 outputs controls the operation of the Analog circuitry. The effects are therefore described in the sub-sections relevant to their destinations.

As this is a multi-purpose converter, designed for use in more than one model of instrument, some of the control lines are not used.

#### 4.5.6 Safety Monitor (Watchdog)

(Fig. 4.5.4)

The watchdog circuits continuously monitor the CPU/SSDA functional process. Detection of a processor malfunction by the watchdog results in the following actions: BARK.

This signal:

- a. removes the drive from the primary of the High Voltage (1kV) transformer,

- b. disables the 400V Power Supply, and

- disconnects the Current Assembly output from the instrument output terminals.

BARK. This is returned as a status bit to the CPU via the SSDA to signal a failure.

BARK DELAYED. This occurs 47ms after BARK and disconnects the AC Voltage Power and Sense circuits from the instrument output terminals.

BARK DELAYED. This disables the registers of the serial/parallel data converters.

The watchdog outputs are manipulated by the power-on are set circuits as follows:

(1) BARK DELAYED and BARK DELAYED are held active for 80ms from power-on and then are allowed to the inactive state only after two SSDA strobes have been detected.

(2) BARK is forced active until CPU/SSDA functioning has been verified; the latter must occur within 470ms of power-on.

(3) BARK is held inactive for 470ms from power-on, after which it provides a FAIL message to the CPU.

Operation of the Safety Reset control on the front panel provides a further 100ms period for the CPU/SSDA functional process to settle, during which time the watchdog circuits must verify correct functioning before its outputs are reset.

The watchdog is tripped if a failure to transmit analog-control updates to the analog circuitry occurs. The updates are of two types:

Transfer of 'Output value' data via the Analog Interface comparators,

Transfer of analog switching data via the SSDA every 40ms.

The CPU generates pulses at 8ms intervals to verify that the correct output value has been latched into the Analog Interface comparators. These pulses are allowed to pass into guard only if the SSDA verifies that the analog switching data is being transferred normally at 40ms intervals. Once in

guard, the pulses prevent the watchdog flip-flops from generating their four BARK and BARK DELAYED output signals; by re-triggering a monostable (M10-4: 18ms).

If two or more pulses are missing, M10 releases the hold, and the watchdog flip-flops 'Bark', activating the safety circuitry. They will be missing if the output value comparators

#### 4.5.6.1 Out-Guard Watchdog

(Circuit Diagrams 430570 Section 7.3 and 430535 Section 7.4)

The CPU verifies the validity of each serial-interface transfer by instructing the SSDA to generate a 'Watchdog Enable' trigger. This pulse, termed W.DOG ENBL SET (M44-7 on p7.3-3), triggers watchdog-enabling monostable M29-11 (p7.3-1).

W.DOG ENBL SET triggering and retriggering extends the natural (470ms) unstable state of M29 indefinitely. Unless the retriggers fail, W.DOG ENABLE at M29-9 remains at logic-Ø. Absence of W.DOG ENBL SET retriggers for longer than 470ms allows M29-9 to restabilize to logic-1.

W.DOG ENABLE is inverted at M43-3 and applied to NAND M46-12 (p7.3-4).

During each successful processor cycle, the CPU addresses M51-9 (Digital Assembly p7.2-2). The resulting low active pulses at 8ms intervals are inverted, and gated with WRT STRB to generate the active-low signal W.DOG at M49-11.

W.DOG travels via the Mother Assembly to the Analog Interface Assembly where it is gated with the W.DOG ENABLE signal at NAND M46 (p7.3-4). The resulting signal at M46-13, W.DOG, consists of positive-going pulses at 8ms intervals when the CPU/SSDA system is working normally, or a logic-1 level if the SSDA fails.

The W.DOG signal travels via the Mother Assembly to be passed into guard on the Reference Divider Assembly (Opto-coupler M9 on p7.4-5).

#### 4.5.6.2 In-Guard Watchdog

(Circuit Diagram 430535 Page 7.4-5)

NOTE: The operating levels of the in-guard CMOS circuits are negatively displaced as follows (nominal voltages):

Opto-coupler output circuits

logic-1: -10Vdc

logic-Ø: -15Vdc

Digital CMOS circuits

logic-1: 0V

logic-Ø: -15Vdc

Level-shifter M36 carries out the interfacing between these two levels.

The signal, W.DOG, is opto-coupled into guard by M9. During normal operation the W.DOG in-guard positive-going 8ms pulses trigger and successively re-trigger the monostable M10-4 to give a continuing logic-Ø at M10-7. The 18ms unstable state of the monostable allows for the absence of one pulse, but the absence of two or more pulses allows M10 to reset, taking M10-7 to logic-1.

The logic level from M10-7 is applied to the set input of flip-flop M13-6. With reset M13-4 at logic-Ø during normal operation, the output conditions of M13-1 and M13-2 are as follows:

(1) Set input M13-6=logic-Ø (no fault); M13-1 (Q)=logic-Ø — BARK not active M13-2 (Q)=logic-1 — BARK not active

(2) Set input M13-6=logic-1 (malfunction); M13-1 (Q)=logic-1 — BARK active M13-2 (Q)=logic-Ø — BARK active

The action of M13-2 changing to logic-Ø, triggers monostable M10-11 which has a relaxation time of 47ms. After 47ms, M10-9 output clocks flip-flop M13-11 to give the command BARK DEL from M13-13 and BARK DEL from inverter M14-12.

are incorrectly updated, or if the SSDA fails to generate 'Transmit' IRQ pulses for a period exceeding 470ms, or if the CPU crashes.

The in-guard watchdog circuits are located on the Referece Divider pcb; the out-guard control signals originate in the Digital pcb and are processed in the Analog Interface pcb.

#### 4.5.6.3 Power-On Reset (Circuit Diagram 430535 Page 7.4-5)

When power is first applied, the build-up of the -15V supply forces shift register M37 Set inputs to logic- $\emptyset$ , but its Reset inputs are held at logic-1 by the charging action of R122/C7.

So M37 is forced into reset state for about 80ms: M37-2 imposes logic-1 at M13-8 Set input.

M37-1 at logic-Ø holds M10 inactive at M10-3, thus preventing random triggering at M10-4 from erratic W.DOG inputs, as the SSDA/CPU functions start up. 'Q' output M10-7 holds M13-6 Set input at logic-1.

Also, the Reset inputs M13-4 and M13-10 are held at logic-1 for a period of 470ms from power-on by the signal FP RST, generated by the power-on reset action of M53 on the Digital Assembly (p7.2-2).

Therefore, the Set/Reset inputs M13-8/M13-10, initially both at logic-1, force M13-13 output to logic-1 to give active BARK DELAYED and BARK DELAYED outputs.

The Set/Reset inputs M13-6 and M13-4, also initially both at logic-1, force:

M13-1 to logic-1 (Active BARK), and M13-2 to logic-1 (Non-active BARK).

The output conditions of M37 (M37-1=logic-Ø, M37-2=logic-1) remain unchanged after the 80ms time constant at M37 Reset inputs, but then M37-11 is free to be triggered from the SSDA strobe input. Two strobe inputs must occur before M37-1 clocks to logic-1 and M37-2 to logic-Ø. M13-13 now changes to logic-Ø, making BARK DELAYED and BARK DELAYED inactive, and the inhibit is removed from M10-3.

The outputs M13-1 and M13-2 remain unchanged until M10-7 fals to logic-Ø by the clocking action of pulses on the W.DOG input. This must occur before M13-4 returns to logic-Ø (at 470ms from power-on) for BARK to be made inactive, otherwise BARK remains active and BARK is set to logic-Ø, giving a fail status bit to the CPU.

#### 4.5.6.4 Malfunction (Fig 4.5.4)

Any malfunction which introduces one of the following conditions will cause the watchdog to bark:

- CPU WRT STRB fails at logic-Ø.

- M51 on the Digital Assembly does not receive the address to activate M51-9.

- c. The SSDA fails to transmit bursts of the W.DOG ENABLE SET pulses to M29 (SSDA is not transferring serial data).

- d. The SSDA Strobe is not triggering M37.

- e. W.DOG pulses are not triggering M10.

In addition to failures at these points, the CPU is informed via SSDA Status byte transfer of certain analog malfunctions. Subsequent CPU action can include deliberate activation of the watchdog by omitting to address M51 as in (b) above.

#### 4.5.6.5 Safety Reset

Once the watchdog has 'Barked' it can be reset, if the malfunction has cleared, by pressing the Safety Reset control on the front panel.

The Safety Reset input to the watchdog circuit, FP RST, is active for 100ms after pressing the Safety Reset key. (M53-9 on Digital Assembly p7.2-2). During this period, the Reset inputs at M13-4 and M13-10 are held at logic-1, allowing the correct pulse inputs from the processor and SSDA to hold M13-6 at logic-Ø, and to reset M13-13 to logic-Ø. The watchdog will not reset if the malfunction persists.

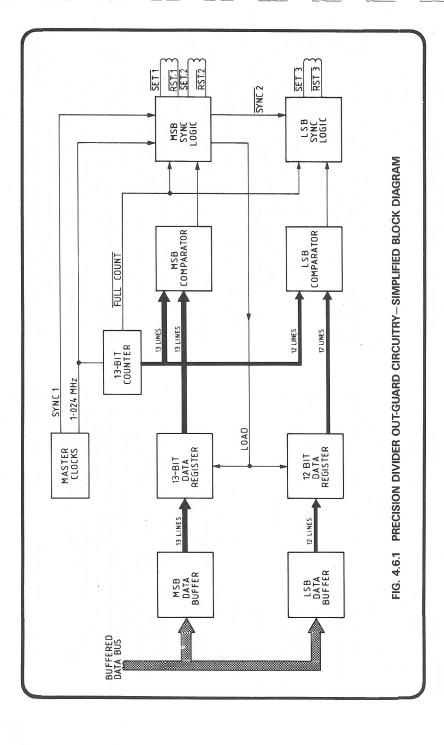

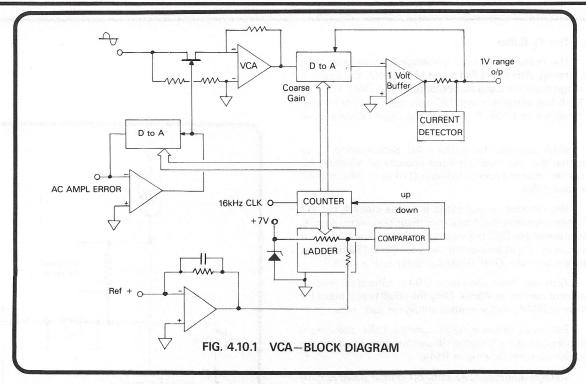

The out-guard circuitry described in this section informs the following functions:

- Receives and latches the demanded output value from the CPU in the form of a 25-bit word.  $\equiv$

- Generates a continuous 13-bit up-count from the 1.024MHz Master Clock (8ms count cycle). (2)

- significant bits of the 25-bit word, generating 'Set' and 'Reset' pulses. These are transferred into guard to trigger the 'Most Significant' JFET switch in the Reference Divider. Compares the 13-bit count with the 13 most-(3)

- Compares the 12 most-significant bits of the count with the 12 least-significant bits of the 25-bit word, generating, 'Set' and 'Reset' pulses. These are transferred into guard to trigger the 'Least-Significant' JFET switch in the 3

The out-guard circuitry is located on the Analogue Reference Divider.

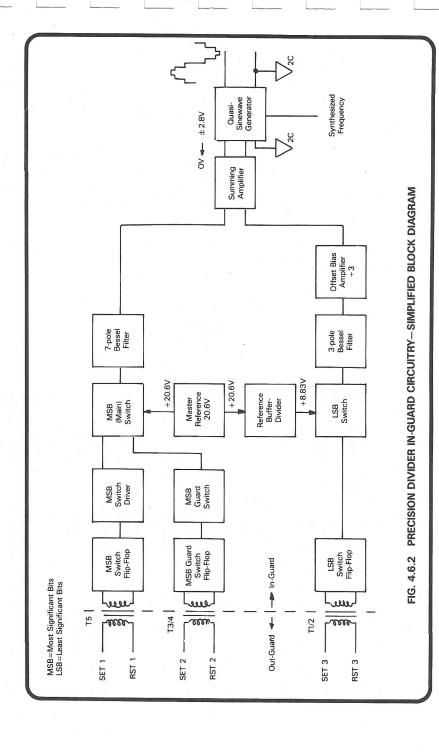

The in-guard circuitry performs the following Interface Assembly.

- JFET switch to generate a square-wave, whose Mark/Period ratio is controlled by the 13 mostwave is smoothed by a 7-pole Bessel filter, to provice a DC voltage whose value varies directly as the Mark/Period ratio of the MSB square-Reference Voltage (20.6V) The squarewhich is chopped by the 'Most Significant significant bits of the 25-bit word. Provides a Master wave. (2) functions:

- Mark/Period ratio is controlled by the 12 least-significant bits of the 25-bit word. The square-wave is smoothed by a 3-pole Bessel filter to provide a DC voltage whose value varies directly as the Mark/Period ratio of the LSB square-Provides a Buffered Reference Voltage (8.83V) JFET switch to generate a square-wave, whose which is chopped by the 'Least-Significant wave. (9)

- AC Assembly as a 'Working Reference Voltage' between 0.126V and 2.79V; whose value is accurately proportional to the value demanded by the CPU's 25-bit word. the 7-pole and 3-pole filters, delivering them via full 4-wire connections to be summed on the Conditions the two DC voltages produced by (

- controlled switching network. It has been given the name 'Quasi-Sinewave'. Digitally generates a stepped AC reference voltage whose peak value is equal to the DC Working Reference Voltage. This gives the RMS Comparator (described in sub-section 4.14) the considerable advantage of comparing AC sense (If AC were compared small DC offsets would magnify and lead to 'DC turnover' errors). The AC waveform against AC Reference. with DC, 8

in-guard circuitry is located on the Reference The in-guard vider PCB Assembly.

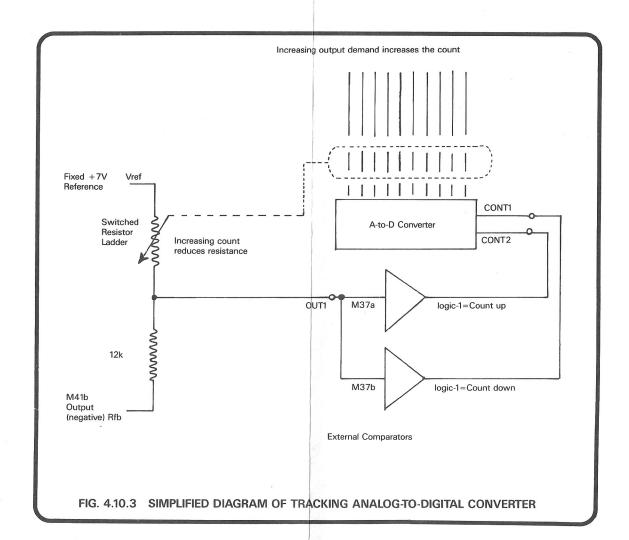

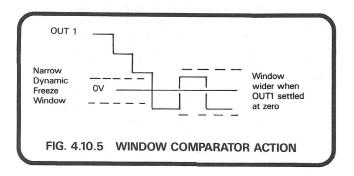

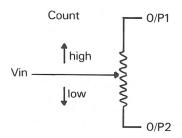

#### **4.6.1.1 General** (Figs. 4.6.1 and 4.6.2)

The comparators are designed as a means of translating a binary word into the accurately defined Mark/Period ratio of a square-wave. The ratio of the square-wave's average value to its peak value subsequently defines the division ratio applied to the Master Reference, and must be adjustable at high resolution.

The required decimal resolution translates into a binary word of 25 bits in length, and each bit needs to exert control of the division ratio.

A single comparator of this length would require more than 30 million clocks to scan, which at sensible clock frequencies would occupy several seconds. To filter out the resultant chopping frequency would require large and expensive components, and force unrealistic operational time-constraints.

In the 4200, by splitting the word into two parts: the 13 most-significant bits (MSB) and the 12 least-significant bits (LSB), a scan-cycling frequency of 125Hz is obtained from a 1.024MHz clock.

Both MSB and LSB comparators are scanned concurrently by the same 13-bit counter, forming two separate square-waves. These act on two separate reference divider switches and filters to generate two separate DC voltages which are subsequently recombined in the AC Assembly.

In summary, the two comparators translate information from the CPU into time-related pulses which control mark/period switching in the reference divider. One comparator translates the 13 most-significant bits of CPU data; the other, the 12 least-significant bits. The comparators perform concurrently, cycling continuously at 125Hz, taking 8ms per full count.

At the start of each 8ms counting period, each comparator generates a SET pulse to start its reference divider 'Mark'. Then after precisely-measured delay times, each generates a RESET pulse to terminate the 'Mark', and start the 'Space'.

At each 8ms full-count, the clock resets and continues up-counting from zero.

#### 4.6.1.2 Comparator Operation (Fig. 4.6.1)

The MSB and LSB Data Buffers are periodically loaded and latched with binary 'Demanded Output Value' data under the control of the CPU.

At the end of each comparator counting cycle, the 13-bit counter FULL COUNT output enables the generation of set pulses SET 1, SET 2 and SET 3 by the MSB and LSB 'Sync Logic' circuits.

FULL COUNT also generates the LOAD command. This writes the data, currently latched in the buffers, into working data latches which form the 13-bit and 12-bit Data Registers, updating the earlier 'Demanded Output Value' priming the comparator.

The MSB and LSB comparators translate this binary data into 'RESET' pulses, whose time relationships to the 'SET' pulses are established by the value of their binary words.

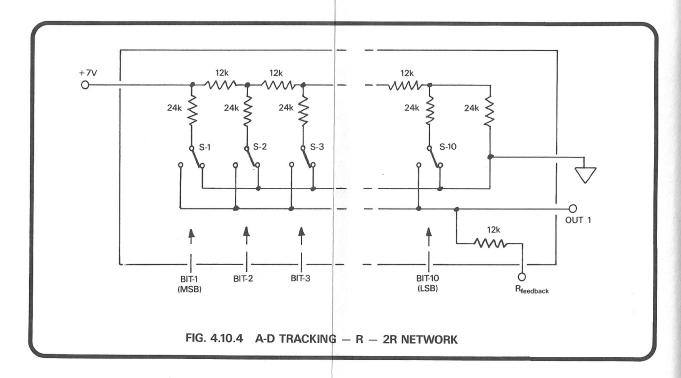

#### 4.6.1.3 13-Bit (MSB) Comparator

(Circuit Diagram No. 430570 Page 7.3-2)

The 13 binary outputs of the up-counter scan the 13 Exclusive-OR elements of the MSB Comparator. With the least-significant bit at 512kHz, and the most-significant at 125Hz, the 8ms scan time thus divides into 8192 time elements, each of 977ns.

Each time element has a unique binary code, incrementing by one bit on its predecessor. When this coincides with the bit-pattern set in the data register, the comparator provides an output pulse to the MSB sync logic. The latter generates reset pulses RST 1 and RST 2 in synchronism with the signal SYNC 1 (2.048MHz).

#### 4.6.1.4 12-Bit (LSB) Comparator

(Circuit Diagram No. 430570 Page 7.3-1)

This functions in the same manner as the MSB comparator, but only 12 bits are scanned over the same 8ms counting period. This accommodates 4096 time elements of 1954ns for each binary increment.

SYNC 2 pulses, generated in the MSB Sync Logic circuitry at half the rate of SYNC 1, synchronize the RST3 output from the LSB Sync Logic.

#### 4.6.2 Comparator Circuit Action

#### 4.6.2.1 Input Data Latches

(Circuit Diagram 430570 Pages 7.3-1 and 7.3-2)

The input buffered data latches M31 to M34 and M37 to M39 receive 27 data bits in four bytes from the buffered data bus. Latches are selected by signals REF DIV 1, 2, 3 or 4 from the memory address decoding on the digital pcb. Data is clocked to the 'Q' outputs of the latches on the positive-going edge of  $\overline{\text{WRT STRB}}$ .

Data from the input latches is used as follows:

25 bits form a data word to the comparator registers M47, M48, M49 (part), M51 and M52. One bit triggers monostable M29 (part), the Q output of which is inverted and buffered to provide the control UPD (OG) used in the relay drive logic for analog switching. One bit, EXT FREQ divided by 10, is not used in the 4200.

#### 4.6.2.2 13-Bit Counter

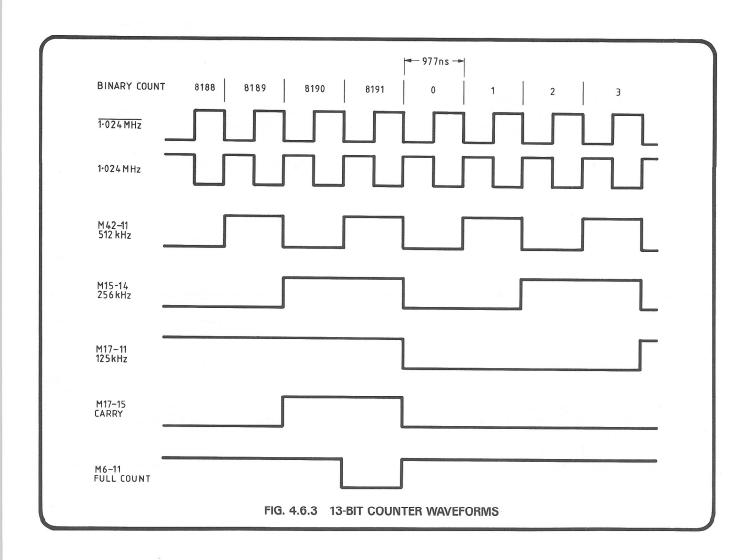

(Circuit Diagram 430570 Page 7.3-2) (Refer to Fig. 4.6.3 for Waveforms)

The counter comprises three 4-bit binary counters M15, M16, M17 and J-K flip-flop M42 (half dual package). The squarewave outputs from the counter are on 13 binary-coded lines, the first (least-significant) being a 512kHz squarewave, the others successively divided in frequency to the most significant output of 125Hz.

Bit 1 is provided by J-K flip-flop M42, which toggles on each falling edge of the 1.024MHz clock to give 512kHz Q and  $\overline{\rm Q}$  outputs. These outputs are used as follows:

- Q and \(\overline{Q}\) complementary outputs together provide the least-significant input to the 13-bit comparator;

- (2) The Q output controls the counting rate of M15, synchronizes M16 and M17, and is used in the gating of FULL COUNT.

Counters M15, M16 and M17 are cascaded as a 12-bit counter and synchronously clocked by the 1.024MHz. M15 counting is enabled only when M42 Q output is logic-1 at the count-enable input M15-7.

As M42 output is at 512kHz, clocking of M15 occurs on the rising edge of alternate 1.024MHz clocks, thus giving outputs of 256, 128, 64 and 32kHz squarewaves from M15.

Counter M16 is enabled by the carry output from M15 together with 512kHz from M42 at the count-enable pins M16-10 and 7 respectively, thus giving outputs of 16, 8, 4 and 2 kHz squarewaves from M16.

Counter M17 functions in a similar manner to give outputs of 1kHz, 500, 250 and 125Hz squarewaves.

The  $2\mu s$ -long carry output from M17 occurs at the end of the 125Hz output when all counter outputs are at logic-1. The carry output is NANDed with M42 Q output to give the  $1\mu s$ -long logic command FULL COUNT. The counting cycle resets and continues, starting from bit 1.

#### 4.6.2.3 13-Bit Comparator Action

(Circuit Diagram 430570 Page 7.3-2)

The 13-bit comparator provides a logic-1 output at TP12 whenever a coincidence occurs between the following two sets of data:

- (1) Data set in registers M47, M48 and M49-1;

- (2) Data from 13-bit counter M42, M15, M16 and M17.

Twelve exclusive-OR elements M25, M26, M27 and three NOR gates of M12 are used to detect a coincidence. The data in the registers is preset by the CPU, while that presented by the 13-bit counter cycles through every binary combination possible on 13 lines.

Two coincident inputs to an exclusive-OR gate provide a logic-Ø to the 12-input NOR gates M24/M23; full coincidence in bits 2 to 13 is shown by a logic-Ø at NAND M13-6. Coincidence at bit 1 is shown by logic-Ø at M12-13 and M12-4 as follows:

| M12 | 2 INPUT | PINS | M12 OUT | TPUT PINS |

|-----|---------|------|---------|-----------|

| 6   | 11      | 9/12 | 4       | 13        |

| 0   | 1       | 0    | 0       | 0         |

| 0   | 1       | 1    | 1       | 0         |

| 1   | 0       | 0    | 0       | 1         |

| 1   | 0       | 1    | 0       | 0         |

only 4 input combinations available

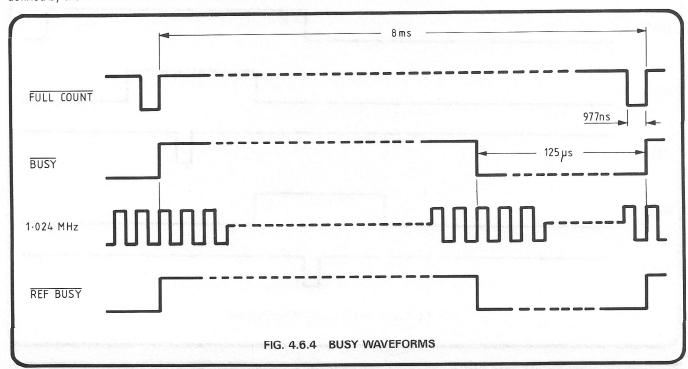

A  $\overline{\text{BUSY}}$  signal is generated by the comparator at NAND M50-13 (TP2) when the 13-bit counter approaches full count. Bits 8 to 13 are at logic-1 for the period of  $125\mu\text{s}$  preceding the end of the counter cycle (see Fig. 4.6.4). The  $\overline{\text{BUSY}}$  level is applied to the D input at M49-9 and is synchronously clocked through as  $\overline{\text{REF BUSY}}$  to buffer M45-2 by 1.024MHz.

As described earlier, the demanded output value is defined by the CPU to a resolution of 25 bits, contained in four

data bytes. The time needed for the 4-byte transfer could allow the latches to contain spurious data until they were fully loaded, and an inaccurate parity could be registered with the counter still running. The counter must not be interrupted, as its full count defines the 'period' of the mark-to-period ratio, which is used to control the division of the reference voltage. It is therefore necessary to reduce the loading time, and this is achieved by double-latching the data.

When the CPU has data to load into the input data latches, it first interrogates the comparator by enabling buffers M45 through REV DIV RD. The REF BUSY signal at logic-1 (M45-3) indicates to the CPU that sufficient time is available for the latch-loading process to take place (at least  $125\mu s$  remain before the LOAD pulse occurs).

If the REF BUSY signal is at logic-Ø, the CPU waits until it returns to logic-1 again.

When the REF BUSY signal is at logic-1, the CPU loads the data by first carrying out four transfers of one byte each into the seven quad buffer latches M31 to M34, and M37 to M39. Each byte's destination is addressed by one of the chip-select signals REF.DIV.1 to REF.DIV.4, which enables the selected buffer latches. The data is latched by the WRT STRB signal.

Once the full 25-bit word has been latched into the buffers, it is available as a single word at the data inputs of the comparator latches M47, M48, M49, M51 and M52. The CPU again interrogates the comparator by REF DIV RD, and five of the elements of M45 buffer the five most-significant data bits back to the CPU.

If parity with the transmitted data is confirmed, the CPU takes no action. When the counter times out, the  $\overline{\text{FULL COUNT}}$  signal is clocked through to M14-6 by  $\overline{\text{SYNC 2}}$  as the LOAD signal, and the new data is transferred into the comparator latches.

If the data latched in the buffers is not as transmitted, the CPU initiates the FAIL 4 message procedure to the operator.

#### 4.6.2.4 'Most Significant Bits' SYNC Logic

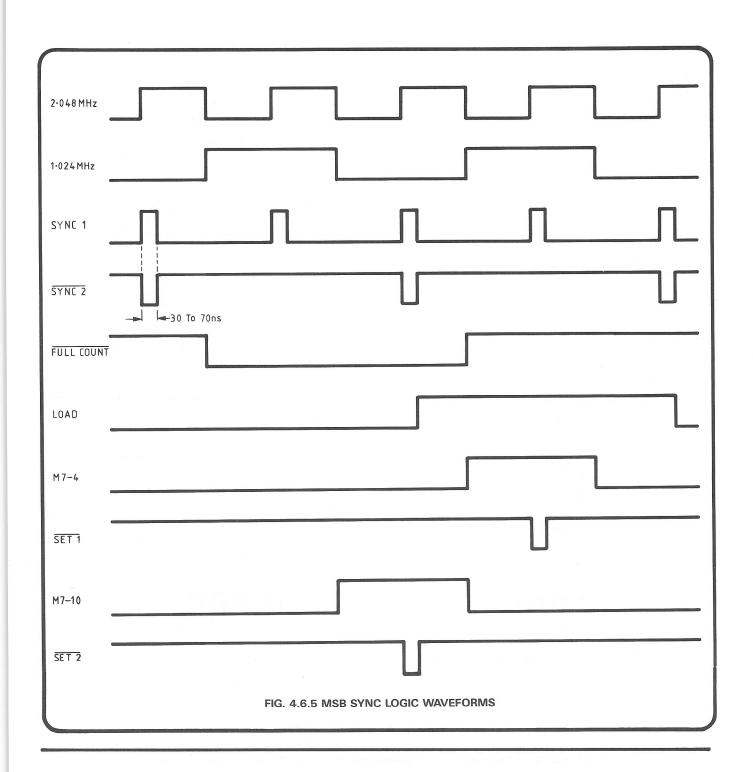

(Circuit Diagram 430443 Page 7.3-2) (Refer to Fig. 4.6.5 for Waveforms)

This circuit, M14, M6, M7 and M8, provides the following signals:  $\overline{\text{SYNC 2}}$ , LOAD,  $\overline{\text{SET 1}}$ ,  $\overline{\text{SET 2}}$ ,  $\overline{\text{RST 1}}$  and  $\overline{\text{RST 2}}$ .

SYNC 2 is obtained by NAND gating 1.024MHz and SYNC 1 to give a synchronizing pulse at half the rate of SYNC 1. (See Fig. 4.6.5).

The LOAD pulse enables the 13-bit comparator registers, and is generated at M14-6 towards the end of the counter's full-count output. FULL COUNT sets the D input

M14-2 and the level is clocked, inverted, from M14-6 by the next two SYNC 2 pulses that occur.

The inverse of LOAD is used to time the pulse SET 1 by NOR gating at M7-4 with 1.024MHz. The pulse at M7-4 is then NAND gated with SYNC 1 to provide SET 1 from M8-1. The pulse SET 2, which occurs 977ns before SET 1, is obtained by gating FULL COUNT with 1.024MHz at NOR M7-10 and then NAND gating at M8-10 with SYNC 1.

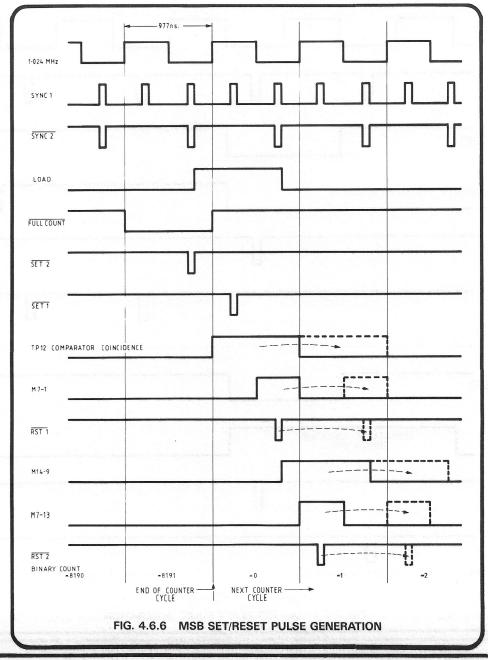

Reset pulse generation (see Fig. 4.6.6) is initiated by a logic-1 level at TP12. This can occur at any one of the 8192 binary counts of the 13-bit counter, the actual time slot in which it appears depends on the binary count at which the coincidence occurs.

The coincidence level at TP12 is NAND gated at M6-8; M6-10 being at logic-1 for all binary counts except 8191. The logic-Ø at M6-8 is NOR-gated at M7-1 with 1.024MHz, this is then used to select the next SYNC 1 pulse via NAND M8-4 to provide the pulse  $\overline{\text{RST}}$  1.

The coincidence level at TP12 is used to set the D input at flip-flop M14-12. This level is clocked to NAND M6-5 by the next \$\overline{SYNC}\$ 2 pulse. NAND input M6-4 is at logic-1 except when LOAD is active, thus M14-9 output is inverted at M6-6 to be NOR-gated with 1.024MHz at M7-13. This is then used to select the next SYNC 1 pulse via NAND M8-10 to provide the pulse \$\overline{RST}\$ 2.

The pulse-timing example given in Fig. 4.6.6 shows the generation of  $\overline{RST}$  1 and  $\overline{RST}$  2 when coincidence occurs in the comparator at binary count = 0 (waveforms in continuous lines).

Coincidence occurring at binary count 1 causes  $\overline{RST1}$  and  $\overline{RST2}$  to increment in time by 977ns with respect to the  $\overline{SET1}$  and  $\overline{SET2}$  pulses (waveforms in broken lines).

RST 1 and RST 2 are generated with the same relationship in time to the comparator coincidence when the latter occurs in any binary count time slot from 0 to 8190 (inclusive).

Note that as the comparator word increments in value, RST 1 and RST 2 increment in time after SET 1 and SET 2, which remain stationary with respect to FULL COUNT and LOAD.

RST 1 and RST 2 are inhibited when coincidence occurs at binary count 8191 to allow for the re-loading of the input registers at the end of the counter cycle. The inhibit is performed by the FULL COUNT level going to logic-Ø and NAND M6-10 which prevents RST 1 being generated, and by flip-flop M14-5 output going to logic-Ø for the period of the load pulse which inhibits RST 2.

# **4.6.2.5 12-Bit Comparator Action** (Circuit Diagram 430570 Page 7.3-1)

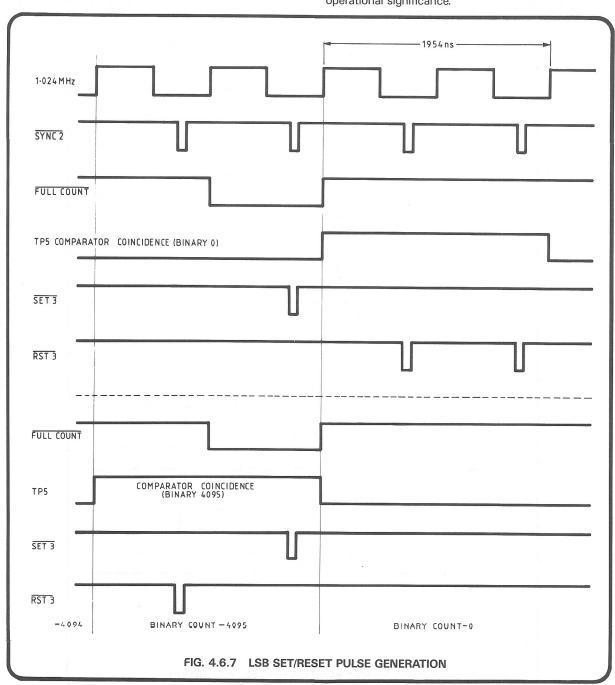

This functions in an identical manner to the 13-bit comparator previously described. Twelve exclusive OR gates, M19, M20 and M21, receive the 12-bit binary output from the common counter and compare these bits with the data in the data registers. The least-significant bit changes at a rate of 256kHz, and the most-significant bit at 125Hz. Coincidence occurring in any of the 4096 binary-count time slots available in the comparator cycle is shown as a logic-Ø at TP5 for a period of 1954ns.

# **4.6.2.6** 'Least Significant Bits' SYNC Logic (Refer to Fig. 4.6.7 for Waveforms)

The timing of SET 3 is controlled by the FULL COUNT pulse from the 13-bit counter. The inverted FULL COUNT at M43-6 is gated with the inverted SYNC 2 from M43-11 to give, at M46-1, SET 3.

The comparator coincidence logic level is inverted to logic-Ø at M12-1; M12-2 being at logic-Ø except when FULL COUNT is low. The waveform at M12-1 is of 1954ns duration and therefore allows two consecutive SYNC 2 pulses to be gated to M46-4 (RST 3).

This condition exists for all  $\overline{RST}$  3 timings except at the binary count of 4095; in this instance, the  $\overline{FULL}$  COUNT pulse occurs after the gating of the first  $\overline{SYNC}$  2 pulse, sets M12-2 to logic-1 and so prevents the second pulse appearing at  $\overline{RST}$  3. In practice, the second pulse of  $\overline{RST}$  3 has no operational significance.

#### 4.6.3 References and Reference Divider

(Circuit Diagrams 430535 Section 7.4) (Refer also to Fig. 4.6.2)

The set and reset pulses from the precision divider comparators control the timing of JFET switches which chop the Master Reference voltages.

The chopped references are filtered to generate two voltages whose levels are proportional to the MSB and LSB squarewaves' mark:period ratio (duty cycle). These MSB and LSB voltages are conditioned, and transferred to the AC Assembly by full 4-wire sensed connection where they are summed at a star-point to generate a Working Reference: 'REF+Ve'.

REF+Ve is adjustable at high resolution (0.03ppm:approx.  $0.6\mu V$  increments), with a maximum possible range of adjustment of 0-20V.

The Reference Divider and Master Reference are also employed in other Calibrators of the series, where the high available resolution is advantageous. In the 4200, however, such resolution is not necessary for the 6½-digit accuracies associated with AC outputs. Also, the basic range is the 1V Range, all other ranges employing either attenuation or amplification. The working reference is therefore reduced to 0.126V to 2.79V by software, which results in a reduction of the maximum mark:period ratio of the chopping waveform to about 0.14.

#### 4.6.4 Master Reference

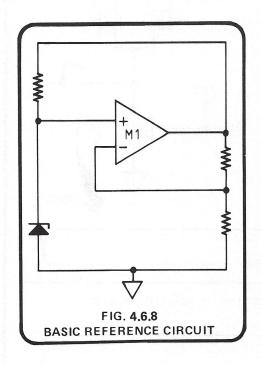

(Circuit Diagram 430553 page 7.4-4) (Refer also to Fig. 4.6.8)

The Master Reference determines the fundamental long and short-term stability of the 4200. It is a separate pcb mounted on the Reference Divider Assembly.

(Refer to the Layout Drawing facing Page 7.4-7)

The basic circuit shown in Fig. 4.6.8 acts as a constant-current generator for a zener reference.

The random character of zener drift in the short-to-medium term may in the long term be regarded as averaging to zero. The averaging action of the four zener diodes on Page 7.4-7 reduces the short and medium term variations (due to drift and noise) by a factor of  $\sqrt{4}$ , effectively twice as stable as a single zener diode.

The diodes and resistors are selected and matched for near-zero temperature coefficient; the overall instrument values are shown together with the stability and accuracy specifications in Section 6 of the User's Handbook.

At manufacture, the zener operating current is adjusted for zero temperature coefficient, by selectively removing links TLA1-5.

The zener voltage of +24.5V at TP3, with respect to Common-R1, is reduced by R24/R25/R26 to +20.6V. This is an approximate value, but it has high temperature and time stability. It is corrected by constants stored in non-volatile memory during calibration. The +20.6V is then buffered by M2 for transmission, at the same value, to the 'Most Significant' Switch in the Reference Divider. Delivery is by sensed connection, the Reference Common-R1 being connected to the Reference Divider Common-4, by a low-resistance wire link from pin A.

## **4.6.4.1 Buffer M2—Temperature Compensation** (Circuit Diagram 430553 page 7.4-7)

In the 4200 instrument, the temperature compensation applied to M2 is adjusted at manufacture by R29 (set TC slope). This adjustment requires specialised test equipment and should not be attempted by users.

If a fault is suspected on the Reference PCB Assembly (400553), contact your Datron Service Center.

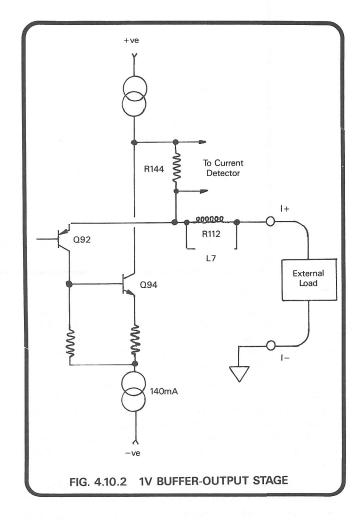

# 4.6.5 Reference Buffer-Divider (Circuit Diagram 430535 page 7.4-2)

R80/81 drop the 20.6V Master Reference voltage (V $_{\rm Ref}$ ) to +8.83 V. M23/Q40 is a voltage-follower providing

+8.83V wrt common-4 at the star-point TP11 to supply the least-significant digit switch.

#### 4.6.6.1 Switch Driver

SET 3 and RST 3 pulses from the LSB Comparator in the Analog Interface Assembly are transferred into guard via pulse transformers T1 and T2, whose centre-tapped secondaries are balanced about Common-4 OV (T1) and +9V (T2).

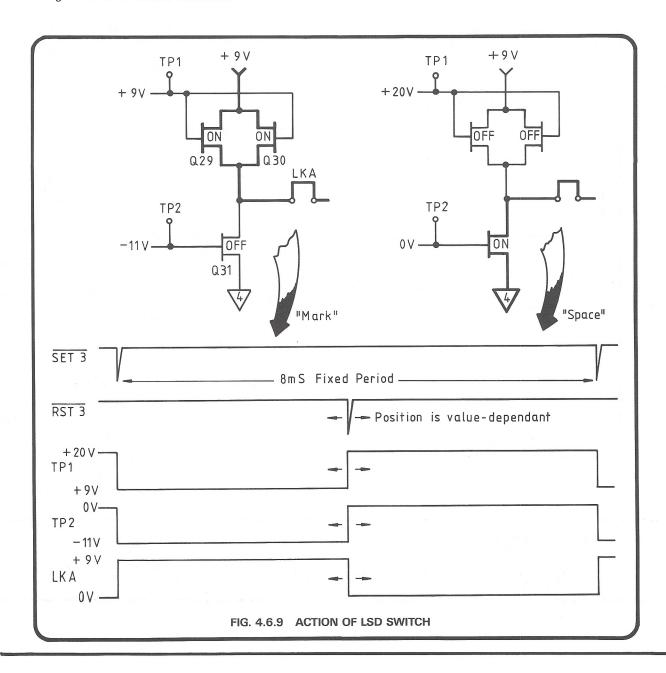

Q5-Q7 form a fast bistable using emitter-coupled logic, to switch TP1 between +9V (mark) and +20V (space).

During the "Mark" time after SET 3 pulse, Q29 and Q30 are switched ON, connecting LKA to +9V Ref. Q1-Q4 have the same bistable action, switching Q31 off during the "Mark" period by -11V at TP2, thus disconnecting LKA from common-4 (OV).

During the "Space" time after RST 3 pulse, Q29 and Q30 disconnect LKA from +9V Ref, and Q1-Q4 switch Q31 on, connecting LKA to common-4 (OV).

Fig. 4.6.9 demonstrates this action.

#### 4.6.6.2 JFET Switch and 3-Pole Filter

The combined action of the switch FETs alternately provides charging current for the 3-pole filter (during 'mark') and discharging current (during 'space').

Two JFETs in parallel (Q29 and Q30) are necessary to equalise the charging and discharging time-constants by matching the "ON" resistances. This preserves linearity of the filter output voltage over the full range of mark/period ratios applied via the set and reset pulses.

The 3-pole filter has the advantage of not being in series with the DC output signal. The 125Hz ripple content is reduced to an acceptable level for the overall instrument specification. The filter output is buffered by voltage-follower M16.

#### 4.6.6.3 Offset Bias Amplifier

M20 performs a dual role:

- (1) Its gain is set to  $\frac{1}{3}$  by  $\frac{R65}{R64}$

- (2) Its output is level-shifted to provide an offset bias for summing (this allows the summed output to have a negative zero offset).

Also a small thermal coefficient zero correction is factory-preset (D10/R85).

M20 transfer function is approximately as follows:

The actual values are as set digitally in software, affecting the mark:period ratio of the JFET switches, using stored calibration constants.

#### 4.6.7 Most-Significant-Bits Switching

(Circuit Diagram No. 430535 Page 7.4-1)

The large reference voltage (20.6V) and the

The large reference voltage (20.6V) and the need for higher resolution makes the MSB Switching circuitry more complex than for LSB; but the principle is the same: the set and reset pulse-timing adjusts the mark:period ratio of the square wave fed to the filter.

The arrangement used for the MSB switching satisfies two essential requirements:

The charge and discharge path resistances for the 7-pole filter must be closely matched. (2) The leakage current of the path switched off must be minimal.

Requirement (1) demands that the matched devices used in both paths are of the same type (P-channel JFETs have approximately 10 times the "on" resistance of N-channel types). But without the voltage standoff and leakage current shunt created by the guard switch, the pinch-off gate voltage for one of the paths would be high enough to generate gate-leakage current in excess of requirements (2).

# 4.6.8 Main And Guard Switches (Fig. 4.6.10) (Circuit Diagram 430535 Page 7.4-1)

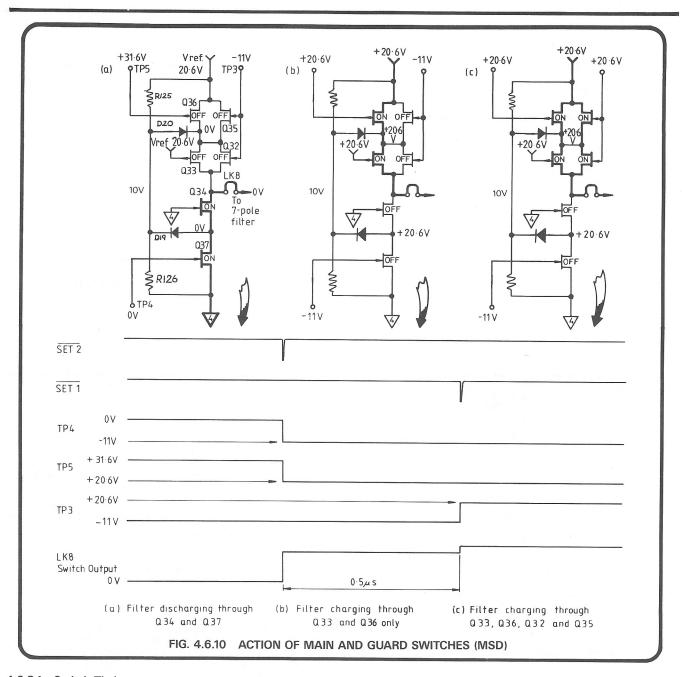

Refer to Fig. 4.6.10, in which only the Space to Mark (SET) state transfer a-b-c is shown.

(The Mark to Space (RESET) transfer is symmetrical c-b-a)

The switch driver flip-flops establish the voltage shown at TP3, 4 and 5 as controlled by the set and reset pulses. The drivers are ECL fast bistables, but note that Q19 and Q20 are included in the main switch driver as a level-shifter for Q32/Q35.

#### 4.6.8.1 Switch Timing

(Fig. 4.6.10)

$$\overline{\rm SET}$$  1 pulse is delayed by 0.5  $\mu s$  after  $\overline{\rm SET}$  2 pulse, and  $\overline{\rm RST}$  2 is delayed by 0.5  $\mu s$  after  $\overline{\rm RST}$  1.

$\overline{\text{SET 2}}$  and  $\overline{\text{RST 2}}$  pulses control the timing of Q36, Q33, Q34 and Q37 in the main switch (TP4 and 5).

SET 1 and RST 1 pulses turn Q35 and Q32 on and off (TP3). Because of the  $0.5\mu s$  delays, Q35 and Q32 conduct only during the time that Q36 and Q33 are also conducting.

#### 4.6.8.2 Filter Discharge Path

In Fig. 4.6.10(a) the switches are in "space" state:

Q37 and Q34 are turned on by TP4 at OV, to provide the filter discharge path. Q33 and Q36 are turned off by TP5 at +31.6V, Q32 and Q35 are turned off by TP3 at -11V.

The filter discharges via resistor R79 and FETs Q34 and Q37. During both Mark and Space periods, R79 (78.7kOhms) is a major determinant of the 7-pole filter charge and discharge currents. Because in 'space' state the 'On' resistances of Q34 and Q37 (3-5 Ohms each) are very small in comparison, the potential at link B can be regarded as zero when considering the effects of the other switching voltages.

Reverse leakage currents in JFET junctions are normally of the order of a few picoamps unless the junction voltages are much in excess of 20V. To control leakage effects from the four JFETs which are turned off, the cathode of diode D20 is connected to the common junction of the four devices. Its anode is returned to the junction of R125 and R126, close to +10V.

The reverse leakage characteristics for a J108 FET (Q35 and Q32) are generally several times heavier than for a J174 (Q36 and Q33). This means that in this switch, the leakage currents via Q35 and Q32 out of the common junction are 4-5 times greater than those entering via Q36 and Q33.

The net leakage out of the junction holds D20 slightly in forward bias, so that its cathode cannot rise above about +10.3V, when the four FETs are turned off in 'space' state. Thus D20 guards the 'buffer' FETs Q33 and Q32 from the effects of the relatively high voltage on Q36 gate. The effects of the buffer FETs' own leakages on the voltage at the filter input can be regarded as negligible, because Q33 leakage currents towards LKB are virtually balanced by those away via Q32.

#### 4.6.8.3 Filter Charge Path

To preserve linearity over the full range of Mark:Period ratios, the filter charging path time constant must closely match that of the discharge path. Q35 and Q32 are factory-selected to form a matched set with Q34 and Q37, all

J108 N-channel FETs (The 'on' resistance of P-channel FETs in a true complementary switch would be much higher: 30-40 Ohms). Nevertheless, to avoid high voltages being developed across Q35/Q32 when changing between states (causing excessive leakage), P-channel FETs are employed. Q36/Q33 are switched on before (and switched off after) Q35/Q32.

Fig. 4.5.10(b) shows this intermediate state after SET 2 and before SET 1, and Fig. 4.6.10(c) shows the fully-conducting state after SET 1. Note that for descriptive purposes, the second step on LKB waveform is heavily exaggerated, and is not readily viewed on an oscilloscope. The slightly longer charging time-constant during this half microsecond, due to the higher resistance of Q36/Q33, is not sufficient to disturb the linearity of the filter in excess of specification.

The voltage between TP4 and LKB during 'mark' state is some 31 volts. In the absence of D19, an adverse voltage distribution c'ould cause excessive reverse leakage in Q37. D19 controls the distribution by limiting the voltage at its cathode to about +10V, constraining Q37 source-gate voltage to a tolerable 20.5V.

#### 4.6.9 7-Pole Filter

(Circuit Diagram 430535 Page 7.4-1)

M26, M28, M32, Q41 and Q42, together with associated capacitors and resistors, form a 7-pole Bessel filter in three active elements; providing approximately 135dB of attenuation at the 125Hz switching frequency and increasing at a rate of 140dB/decade. This allows sufficient bandwidth to avoid excessive settling time while reducing the output ripple to within instrument specification. Q41 and Q42 source-followers provide input bias currents for M26 and M28

from the 15V supplies, and buffer the line from bias-current effects. M32 bias-current effects are insignificant.

The filter output at TP13 is fed to a buffer amplifier as '+Ve SUMMING AMP', to be subsequently added to the output from the Least-Significant Switch offset-bias amplifier. R101 and C51 prevent spikes from the chopper-stabilized buffer amplifier being fed back into the filter.

#### 4.6.10 Summing Amplifier

(Circuit Diagram 430535 Page 7.4-3)

#### 4.6.10.1 '+VE SUMMING AMP' Buffer

M33, M34 and Q44 buffer the '+Ve SUMMING AMP' voltage output from the 7-pole filter (this is proportional to the Mark/Period ratio of the 13 most-significant bits of the binary word which defines the instrument output value demand).

M33 is a high-gain, chopper stabilized integrator with a bandwidth of approximately 10Hz, and Q44 provides additional bandwidth for rejection of HF common-mode noise.

M35, D14, D15, Q48 and Q49 generate bootstrapped supplies to preserve full dynamic-range linearity. Q46 and Q47 establish 3mA constant-current drives for D14 and D15

The whole amplifier acts as a voltage-follower, M34/Q45 providing the output drive, buffering the output of M33 and Q44. The output is delivered as 'Hi O/P' to the AC Assembly via RL2 (RL1 being permanently de-energized in the 4200). The output is sensed in the AC Assembly to account for the volts-drops in the connecting circuit. The sense feedback voltage 'Hi SENSE' is applied to the inverting input of the whole buffer via R98.

For a zero count in the MSB comparator, the filter output voltage is approximately +3.2mV, and a full count of 8191 would produce +20.6V. These are the voltages which are developed at the buffer output.

#### 4.6.10.2 '-VE SUMMING AMP' Buffer

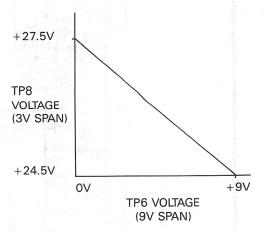

M38, M39 and Q51 buffer the '+Ve SUMMING AMP' voltage output from the Offset Bias Amplifier derived from the 3-pole filter (this is proportional to the Mark/Period ratio of the 12 least-significant bits of the binary word which defines the instrument output value demand).

The dynamic range of the filter output voltage was originally defined by the Reference Buffer (8.83V) for efficient operation of the FET switching circuitry.

It was scaled in the Offset Bias Amplifier to give +27.5V for an LSB comparator count of zero (from approx. +1.1mV at TP6), and +24.5V for a full count of 4095 (from +8.83V at TP6). It now needs to be scaled down so that its proportionality to the '+Ve SUMMING AMP' dynamic range is correct.

R99 and R100 attenuate the '-Ve SUMMING AMP' input voltage by a factor of  $0.8545\times10^{-3}$ . At zero count, +27.5V is reduced to +23.5mV, and at full count +24.5V reduces to +20.9mV. These are the extremes of voltage developed at the buffer output.

The whole amplifier acts as a voltage-follower, but without bootstrapped supplies (the small input voltage dynamic range of approx. 2.5mV does not warrant it). Otherwise the circuit is identical to the '+Ve SUMMING AMP'. M39/Q52 provide the output drive, buffering the output of M38 and Q51. The output, 'Lo O/P', is delivered via RL2 to be sensed in the AC Assembly. The sense feedback voltage 'Lo SENSE' is applied to the inverting input of the whole buffer via R127.

#### 4.6.10.3 Summing

On the AC Assembly, the outputs from the two buffers are summed by defining the 'Lo O/P' level as 'Reference Common' (Common 2C), and the 'Hi O/P' level as 'REF +Ve'. Thus the voltage at 'REF +Ve' with respect to 'Reference Common' will always be 'Hi O/P' minus 'Lo O/P' at their current values.

The reference voltages and reference division circuitry are chosen to allow for software calibration adjustments, so the span of the summing amplifier overlaps the possible full Span of 0 to 19.999999V at both extremes:

With an overall 25-bit count of zero in the comparators, REF+Ve is +3.2mV minus +23.5mV, a negative overlap of -20.3mV.

At overall full count, REF+Ve is  $\pm 20.6$ V minus  $\pm 20.9$ mV, approximately  $\pm 20.5$ 8V.

#### 4.6.10.4 Bipolar Reference Switching

Relays RI1 and RL2 are used in DC calibrators for polarity reversal. This is not necessary in the 4200, and during operation RL1 is always de-energized, while RL2 is energized. Thus all outputs from the summing buffers are fed to the AC Assembly via RL2.

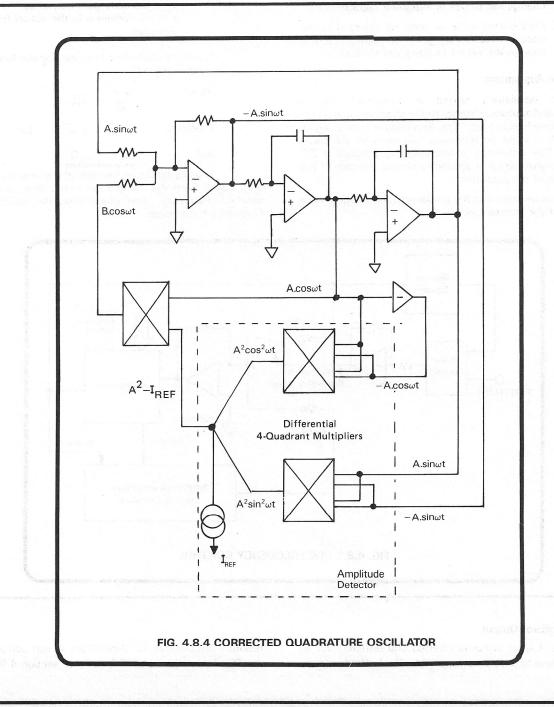

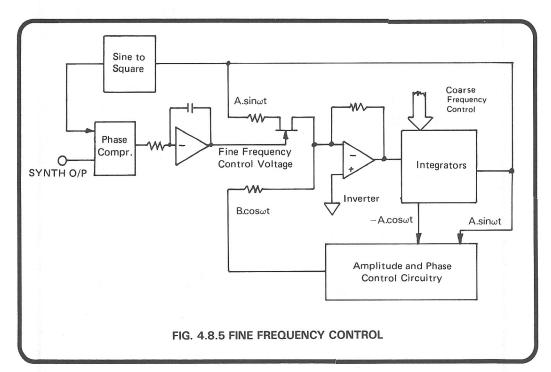

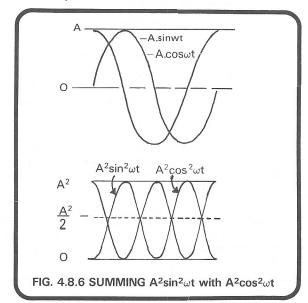

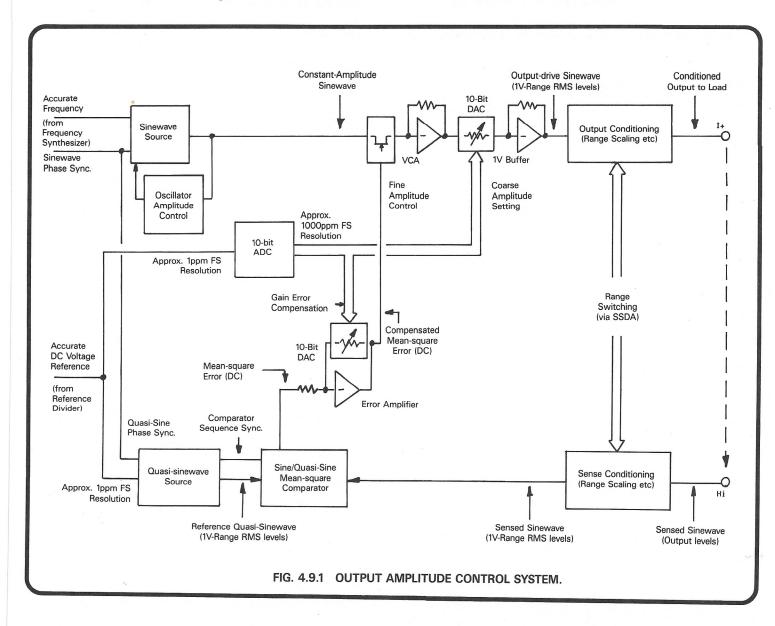

#### 4.6.11 Quasi-Sinewave Generation

#### 4.6.11.1 Quasi-Sinewave Reference

In the Sense/Reference comparator, a considerable advantage is gained by comparing AC with AC. (If AC sense were compared with DC reference, small DC offsets would be magnified, leading to 'DC turnover' errors). The AC waveform used as reference is constructed in ten steps by a digitally controlled switching network, based on the DC reference as its peak value. It has been given the name 'Quasi-Sinewave'.

The comparator produces an error to drive the VCA, which is proportional to the difference in 'Mean Square' values, and is driven to zero by the action of the Output-Sense loop. At zero error the RMS value of the comparator's sense input has thus been adjusted by the loop to be equal to the RMS value of its reference input.

On the 1V Range there is neither amplification nor attenuation in the Output-Sense loop. The quasi-sinewave is designed so that with the 1V Range selected, its RMS value is equal to the voltage demanded on the front panel OUTPUT display, (with small, controlled adjustments for calibration).

On higher ranges, decades of amplification are switched in to set the output to the demanded voltage. Switched decades of attenuation reduce the sensed sinewave back to the 1V-Range level for comparison with the quasisinewave.

On millivolt ranges the 1V sense loop is used with precise, passive, decade attenuators reducing the output to the values on the display.

On current ranges, the current reference is derived from either the closed 1V or 10V Range Output/Sense loop.

Therefore on all ranges the Output/Sense loop gain is driven to a magnitude of 1, so that the VCA and the comparator both operate at 1V Range levels.

#### 4.6.11.2 4200 DC Reference Scaling

The Reference Divider hardware is common to several instruments. In DC calibrators, the basic voltage range is usually the 10V Range, with 100% overrange at Full Scale. In these cases the full span of reference values is employed, generating the resolution necessary to accommodate the DC accuracy available.

The same accuracy is not available for AC, so the high resolution is not necessary. Moreover, the linearity of the analog circuitry is improved by using a smaller dynamic range in the reference circuits. So in the 4200 the 1V Range is the basic range, and the software scales its demanded value accordingly.

In the 4200 the sensed output is compared against the quasi-sinewave whose characteristics match those of the sensed sinewave. To construct the quasi-sinewave, the DC reference voltage needs to be set at its peak value.

The microprocessor program imposes, in software, the scaling factors which establish the reference voltage at the peak value of the quasi-sinewave. Thus the full span of the 25-bit comparator, and hence the possible dynamic range of the DC reference, are realized only at times when the Reference Divider itself is being calibrated. Before initial calibration, the maximum obtainable reference voltage is slightly greater than 2.8V, and the minimum is slightly less than 125mV. This overlaps the peak voltages of the quasi-sinewaves corresponding to the maximum and minimum values of sensed output; giving a margin for accurate calibration, from digital gain factors held in the non-volatile calibration memory.

#### 4.6.11.3 DC Reference Voltage Values

As mentioned earlier, the DC Reference is used to establish the amplitude of the quasi-sinewave. When the 1V Range is selected, the reference is set to the peak value of the quasi-sinewave, which is 1.397 times the demanded RMS (sinewave) voltage output of the instrument. In normal use, therefore, the reference voltage is adjusted by front panel OUTPUT display selections; between 125.7mV (for 0.9V selection) and 2.79V (for 1.999999V selection), plus or minus any user-calibration corrections.

On higher and lower ranges, analog range switching in the sense amplifiers scales the sense voltages for comparison with the same voltage span of quasi-sinewaves.

# 4.6.11.4 Reference Inverter

(Circuit Diagram 430447 page 7.7-2)

The quasi-sinewave is derived by a specific form of D-A converter, selecting voltages from a divider network. Because negative values are required, the divider is strung between positive and negative reference voltages; the unitygain Reference Inverter generates the negative reference 'REF-Ve' by inverting 'REF+Ve'.

M1, M2 and Q1 perform the inversion. M2 generates the bandwidth necessary for amplitude switching operations, while chopper-stabilized integrator M1 removes DC offsets, always referring the inverter output to Common-2C. To compensate for RMS value changes in the quasi-sinewave (due to switching errors arising from frequency changes), feedback from the quasi-sinewave is applied via R1, C4, R4 and C5. Q1 provides the output drive to the quasi-sinewave generator.

# 4.6.11.5 Quasi-Sinewave Generator

(Circuit Diagram 430447 page 7.7-3)

The SYNCØ input to M11 RESET is a decoded address which, when set to logic-1, disables the Quasisinewave sequence counter M11. It is permanently held at logic-Ø in the 4200, to enable the quasi-sinewave for both AC Voltage and Current functions.

The quasi-sinewave is generated at a frequency determined by the Frequency Synthesizer 100Hz-4kHz output (para 4.7.3.3 describes the synthesis), clocking the decade counter M11 via J7.50. This continuously recycles M11 in ascending count through  $\Omega_{g}$  to  $\Omega_{g}$ , ten clocks constituting one cycle of the quasi-sinewave. So the quasi-sinewave runs at a frequency of between 10Hz and 400Hz, indeed the carry  $C_{out}$  of M11 returns to the Synthesizer via J7-51 to be selected as the reference frequency for the 100Hz (10-330Hz) frequency range.

With increase of frequency range, the difference between the frequencies of output and quasi-sinewave increases in decade steps. As the comparison of sense and quasi-sinewave signals is performed at mean-square DC levels, this difference theoretically does not matter, so long as the signal is at an exact multiple of the quasi-sinewave frequency. However, to achieve optimum operation of the Sense/Reference comparator, the zero crossings of the quasi-sinewave are synchronized to occur coincident with a sense signal zero crossing.

Synchronization is achieved by the clock input to M9, controlling the timing of the quasi-sinewave switches M8 and M14. Using the same clocks, M11 and M10 transit times prevent the data from arriving at M9 'D' inputs until the data already established there by the previous clock pulse has been latched at its outputs. Thus data ripples through M11 and M9 at successive clock pulses.

The ripple rotates the data by one clock period and would, if left uncorrected, put the switching out of sequence. The arrangement of the connections between M11 outputs and M9 data inputs, combines appropriate outputs so as to correct the switching pattern. The table in Fig. 4.6.11 demonstrates the rotation of 1 clock period; the quasisinewave steps being labelled at M9 inputs and outputs.

The quasi-sinewave is output to the transfer switching input to the Sig/Ref comparator at M16-1. The action of the transfer switch is described in section 4.14.

A second output is filtered and fed back as compensation to the Reference Inverter as described earlier (para 4.6.11.4).

| 0    |                           |                               |                              |                                         |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                           |

|------|---------------------------|-------------------------------|------------------------------|-----------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 6    | Q <sub>8</sub>            | 10                            | 02                           | 5                                       | -0.42                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ,                         |

| 8    | Ω7                        | ဗ                             | ΟØ                           | 9                                       | -1.16                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                           |